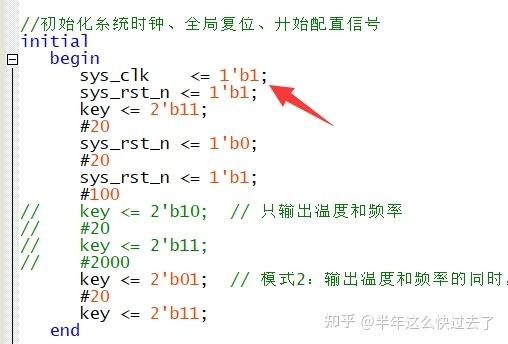

在Verilog编程中,遇到报错提示“缺少左括号”通常意味着在你的代码中存在括号不匹配的问题,这种错误会导致编译失败,因为Verilog编译器需要括号来正确解析表达式、语句块和模块端口列表等,以下详细解释这个错误的原因以及如何解决它。

理解Verilog中的括号是非常重要的,在Verilog中,括号用于定义运算的优先级,控制代码块的开始和结束,以及函数调用的参数列表等,以下几种情况是常见的需要使用括号的地方:

1、算术表达式中的括号用于明确指定计算的顺序。

2、条件语句和循环语句中的括号用于定义条件或循环的控制逻辑。

3、模块实例化和函数调用中的括号用于列出端口连接或参数。

如果出现“缺少左括号”的错误,通常意味着以下几种情况之一:

你确实遗漏了一个左括号。

你可能在某处错误地放置了一个右括号。

你的代码中的注释或字符串字面量可能包含了不匹配的括号,编译器可能将其误认为代码的一部分。

你可能在代码的某个地方插入了不必要的字符,比如多了一个右括号。

下面是如何解决这个问题的详细步骤:

1、检查错误提示:编译器通常会给出错误所在的行号和列号,这是寻找问题的第一站,检查那一行的代码,看看是否有明显的括号缺失或错误。

2、检查括号匹配:从报错位置开始,向前和向后检查代码,确保每个左括号都有一个对应的右括号,注意,括号可以嵌套,因此需要逐对检查。

3、检查注释和字符串:确保在注释和字符串字面量中的括号是匹配的,有时候注释中的括号可能会被编译器错误地解释为代码的一部分。

4、逐步排查:如果错误不是立即显而易见的,可以从报错位置开始逐步注释掉代码块,直到错误消失,这样可以定位到问题所在的代码区域。

5、使用代码格式化工具:有时候代码格式化工具可以帮助你检查和修复括号不匹配的问题,这些工具还可以帮助你整理代码,使得括号和代码结构更加清晰。

6、人工审查:细致地审查代码,尤其是那些复杂的表达式、条件语句和循环,手工检查每一对括号是否正确打开和关闭。

7、查看上下文:括号错误可能由于上下文中的其他错误(如语法错误)而触发,确保没有其他语法错误干扰了括号的匹配。

8、代码审查:如果自己难以找出问题,可以寻求同事或同学的帮助,第二双眼睛有时候可以发现你没有注意到的问题。

9、简化问题:如果问题依然存在,尝试简化引起问题的代码块,将复杂的表达式分解为简单的部分,单独测试每个部分,这样可以更容易地识别问题。

10、编译器警告:一些编译器可以提供更严格的警告设置,可以帮助你识别潜在的问题,包括括号不匹配的警告。

通过上述步骤,应该能够定位并修复“缺少左括号”的错误,如果问题依然存在,可以尝试重建整个代码环境或联系编译器的技术支持以获取进一步的帮助。

记住,良好的编程习惯包括在编写代码时始终保持警惕,并经常进行编译检查,这样可以及早发现并修复这类问题,编写清晰、格式整齐的代码也可以减少这类错误的发生。