Vivado 2015是一款由Xilinx公司开发的集成设计环境,广泛用于FPGA的设计和仿真,在使用Vivado 2015进行仿真时,可能会遇到各种报错,以下是一些常见的报错及其解决方法,供您参考。

ambiguous clock in event control

问题描述:在always块中,当使用posedge和negedge同时作为敏感列表时,可能会导致时钟信号模糊。

解决方法:检查always块中的敏感列表,确保时钟信号和复位信号的使用是明确的,如果不需要使用复位信号,可以将其从敏感列表中移除。

reg [31:0] Fword; reg [31:0] Fwordr; always @(posedge Clk or negedge Resetn) Fwordr <= Fword;修改为:

reg [31:0] Fword; reg [31:0] Fwordr; always @(posedge Clk) Fwordr <= Fword;Common 1739

问题描述:在运行仿真时,可能会遇到Common 1739错误,导致仿真无法进行。

解决方法:检查Tcl控制台输出或相应的日志文件(如elaborate.log),以获取详细的错误信息,根据错误信息,定位问题所在,并解决,常见的问题可能包括:

1、仿真测试平台中的连线错误,检查Testbench中的信号连接是否正确。

2、模块端口未正确例化,检查模块例化时的端口连接是否遗漏或错误。

cannot open verilog file

问题描述:在重新打开Vivado项目时,可能会出现无法打开Verilog文件错误。

解决方法:

1、检查编译顺序(Compile Order)中是否出现了错误的文件或重复的文件,如有,删除不需要的文件或修改文件路径。

2、确保Verilog文件存在于项目路径中,且没有移动或重命名。

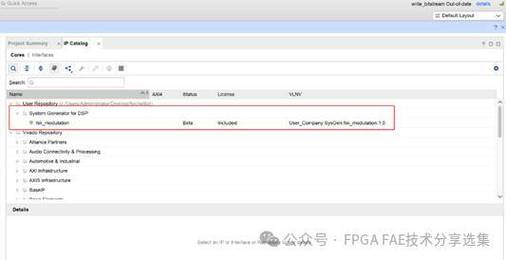

DCP does not exist

问题描述:在综合工程时,某些IP文件可能无法找到,导致DCP(Design Check Point)文件不存在。

解决方法:

1、检查IP文件是否被误删或移动,将其重新添加到项目中。

2、如果项目路径过长,可能会导致问题,尝试将项目移动到较短的路径,例如D盘根目录。

debug hub core时钟检测不到

问题描述:在使用JTAG仿真器抓取信号时,可能会出现debug hub core时钟检测不到的错误。

解决方法:

1、确保ILA和DEBUG模块的时钟频率高于JTAG仿真器的频率,根据Xilinx官方文档,至少应为JTAG速率的1.8倍。

2、如果debug hub core的时钟频率低于JTAG仿真器的频率,可以尝试以下方法:

降低JTAG仿真器的频率。

提高debug hub core的时钟频率,修改XDC约束文件中的相应部分。

注意:ILA和DEBUG模块会占用FPGA资源,可能影响用户逻辑的时序,在实际项目中,需要权衡时钟频率和资源占用。

在遇到Vivado 2015仿真报错时,要仔细分析错误信息,定位问题所在,并根据具体情况采取相应的解决方法,了解Vivado的版本更新和官方文档也是解决问题的关键,希望以上内容对您有所帮助。